我们知道,Intel Xe GPU架构分为四个层级,或者说四种微架构,其中以上是的Xe LP低功耗版仅供核显、入门独显,即将到来的Xe HPG高性能图形版面向中高端游戏显卡,Xe HP高性能版适合加速计算、AI、ML等但所知最少,Xe HPC高性能计算版则是最顶级的存在,主攻大型数据中心、超算。

,这里来看看Xe HPC和首款产品Ponte Vecchio,竞争对手是NVIDIA A系列、AMD Instinct系列。

当然,它们距离普通人非常非常遥远,但却是技术实力的最高体现。

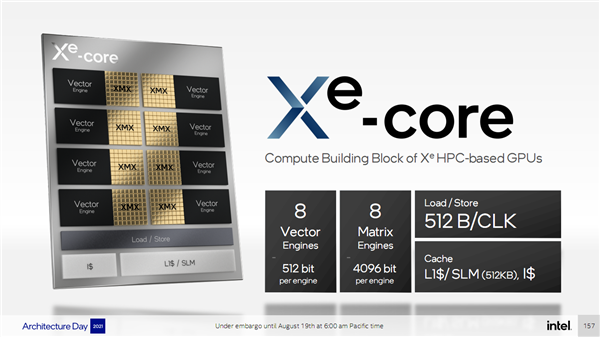

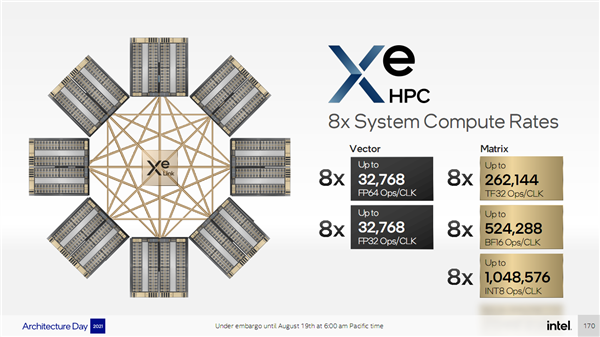

矢量引擎每时钟周期可执行256个FP32、256个FP64、512个FP16等数据操作,矩阵引擎则每时钟周期支持2048个FP32、4096个FP64、4096个BF16、8192个INT8。

与矢量引擎、矩阵引擎搭档的,是一个更宽的宽加载/存储单元,每个时钟周期取回512字节数据。

,而且可以通过软件配置作为暂存区使用,又称共享内部显存。

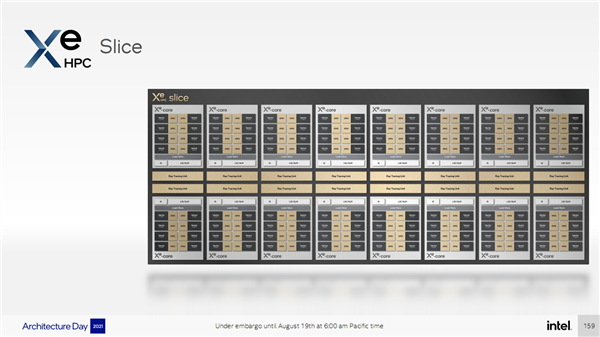

Xe核心的上一层级叫做“切片”(Slice),不同于Xe HPG上的渲染器切片(Slice),毕竟一个是做计算,一个是做图形渲染。

,四倍于Xe HPG渲染切片的规模,同时还有8MB一级缓存、16个光追单元、一个硬件上下文(Hardware Context)单元,其中光追支持光线遍历、边界框相交、三角形相交,提供固定函数计算。

硬件上下文单元大家可能比较陌生,它能让GPU同时执行多个应用,而无需昂贵的基于软件的文本切换。

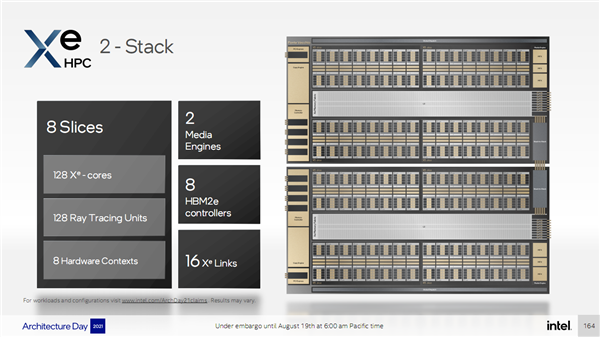

切片的上一级则是“堆栈”(Stack),至此才算一个完整的GPU。

同时,堆栈内还有大规模二级缓存、4个HBM2e内存控制器、1个媒体引擎、8个Xe链路,以及拷贝引擎、PCle控制器。

Xe HPC架构是可以轻松扩展的,支持多堆栈设计,属于业内首创,依靠的是EMIB封装和堆栈间互连通道,可保持堆栈之间的内存一致性。

比如这是双堆栈,整体规模直接翻番,它就是后边要说的首款Ponte Vecchio,但看架构图,似乎不支持四堆栈。

,算力直接暴力乘以8。

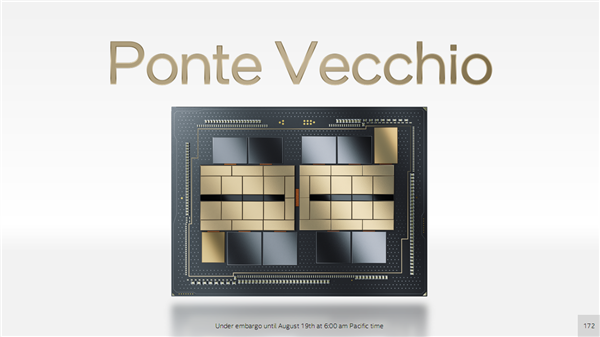

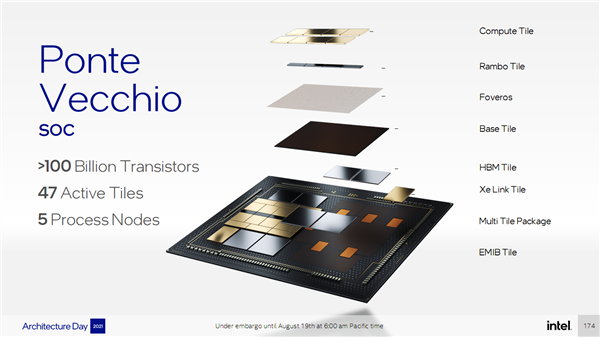

Ponte Vecchio作为基于Xe HPC架构的首款产品,一切的一切都是全新的,包括验证方法、软件、可靠性方法、信号完整性机制、互连、供电、封装、I/O架构、内存架构、IP架构、SoC架构。

如此复杂的芯片设计,面临的挑战自然是空前的,首席架构师Masooma Bhaiwala直言这是她30年来设计的最复杂的芯片,堪称制造奇迹。

其中,Foveros 3D封装是一个关键,最终的数据传输速度不得不提高到最初规划的1.5倍,以便以把Foveros连接数量降至最低,但依然比之前任何设计都高了两个数量级。

开发团队还必须在设计初期就锁定Foveros在所有单元上的位置,这意味着必须一开始就搞定整个平面图布局,中途也不允许有明显变更。

芯片设计和验证也是全新流程,为此开发了大量新的工具、方法、脚本,并独立安排4个主要单元,开发各自的调试软件包,分而治之,加速开发,最终在SoC整体封装完成几天内就成功启动,运行了Hello World。

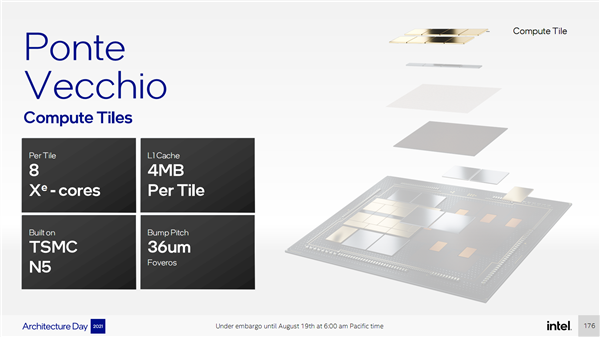

再来看几个关键的部分,计算单元采用台积电N5 5nm工艺,每个集成8个Xe核心、4MB一级缓存,Foveros封装凸点间距36微米。

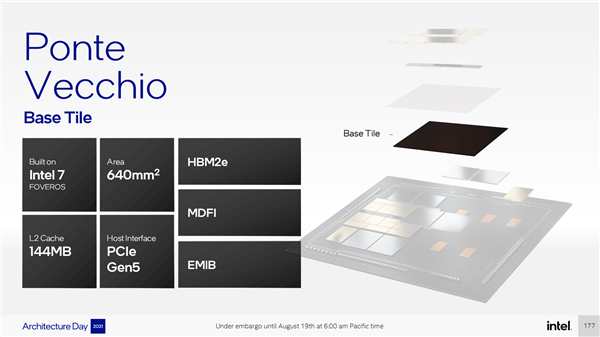

,包括PCIe 5.0总线、HBM2e内存、MDFI链路、EMIB桥接,几乎是在挑战物理极限。

它采用Intel 7工艺、Foveros封装,面积达640平方毫米,集成了多达144MB二级缓存。

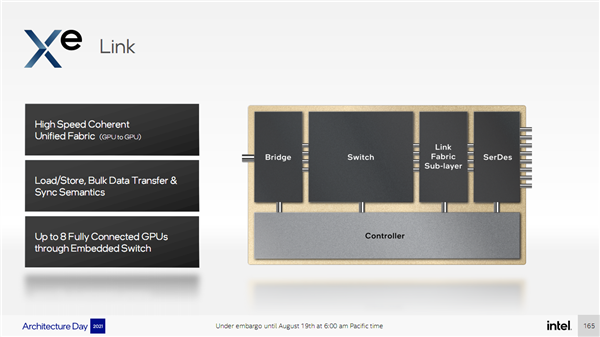

,负责不同GPU之间的连接,是面向HPC、AI的纵向扩展的关键,每个单元有8条,实现了最高90G Serdes,可以满足“极光”(Aurora)这样百亿亿次级级超级计算机的需求。

Ponte Vecchio目前处于A0版本阶段(一般到A1就投入量产),成功运行了数百个工作负载,实测FP32吞吐性能超过45TFlops,Memory Fabric缓存带宽超过5TB/s,互连带宽超过2TB/s。

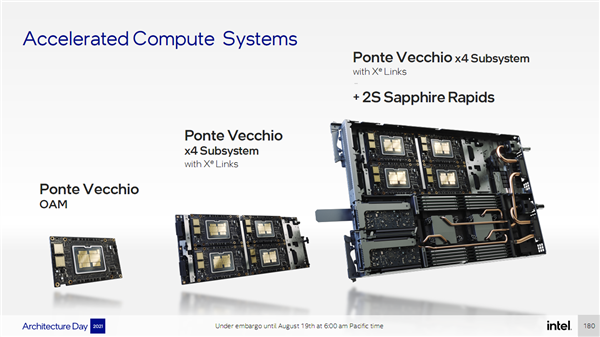

Ponte Vecchio将有多种产品形态,最基本的单芯片做成OAM模块,集成到一个载体基板上,AMD Instinct也有这种。

,就是一个超算节点,将用于“极光”超算。

支付宝扫一扫

支付宝扫一扫 微信扫一扫

微信扫一扫