今年底AMD很有可能发布增强版的7nm Zen3处理器,为了对付Intel的12代酷睿Alder Lake,它将用上3D V-Cache缓存技术,额外增加了128MB缓存,总计192MB。

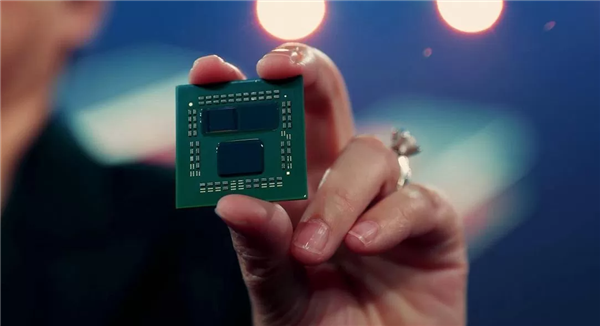

该技术今年6月份台北电脑展上首次公布,展示用的是一颗锐龙9 5900X 12核心处理器,原本内部集成两个CCD计算芯片、一个IO输入输出芯片。

经过改造后,它的每一个计算芯片上都堆叠了64MB SRAM,官方称之为“3D V-Cache”,可作为额外的三级缓存使用,这样加上处理器原本集成的64MB,总的三级缓存容量就达到了192MB。

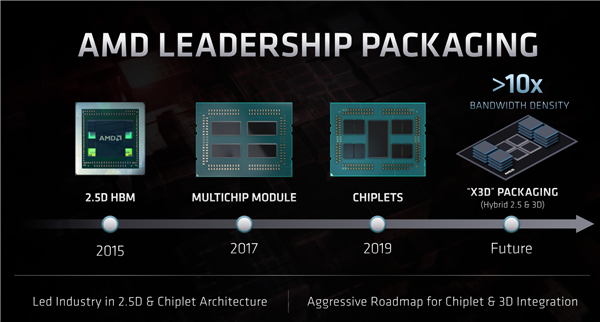

AMD在其中应用了直连铜间结合、硅片间TSV通信等技术,实现了这种混合式的缓存设计。

根据AMD的数据,改进之后,对比标准的锐龙9 5900X处理器,频率都固定在4GHz,3D V-Cache缓存加入之后,游戏性能平均提升了多达15%。

对于该技术,Techinsights的研究员Yuzo Fukuzaki日前公布了更多细节,称AMD已经研究该技术多年,使用了TSV硅通孔技术将额外的128MB缓存集成到芯片上,面积6x6mm,带宽超过2TB/s。

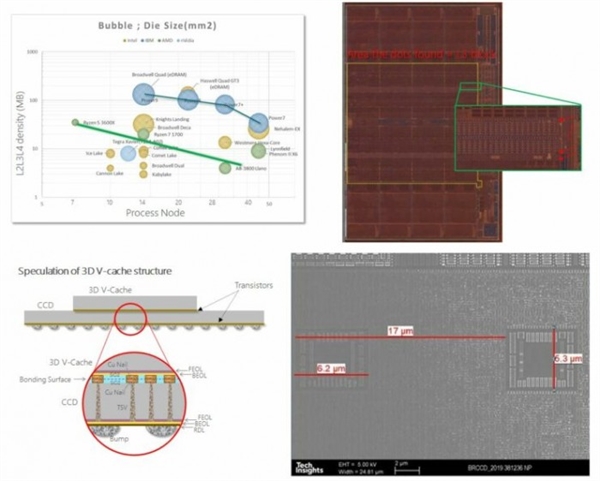

他在文章中指出,为了应对memory_wall问题,缓存内存的设计很重要,这是缓存密度在工艺节点上的趋势,逻辑上的3D内存集成可以有助于获得更高的性能。

随着AMD开始实现Chiplet CPU整合,他们可以使用KGD(Known Good Die)来摆脱模具的低产量问题。在IRDS(International Roadmap Devices and Systems)中,这一创新预计将在2022年实现。

TechInsights以反向方式深入研究了3d V-Cache的连接方式,并提供了以下发现的结果:

TSV间距:17μm

KOZ尺寸:6.2 x 5.3μm

TSV数量:粗略估计大约23000个

TSV工艺位置:在M10-M11之间(共15种金属,从M0开始)

支付宝扫一扫

支付宝扫一扫 微信扫一扫

微信扫一扫