五月初,IBM宣布2nm工艺制程取得重大技术突破引发一番热议,提醒业界5nm处理器已经大规模市场化,芯片巨头们也已进入下一轮制程竞赛:三星披露其即将推出的3nm工艺将基于下一代晶体管类型全栅极(GAA)FET,台积电也计划将FinFET扩展到3nm,然后到2024年左右迁移到2nm的纳米片FET。

一直以来,芯片巨头都将先进制程作为竞争的目标,一方面是将摩尔定律奉为圭臬,力争做到功耗、性能和面积(PPA)的平衡,另一方面随着节点命名规则的混淆,先进制程逐渐演变为厂商的营销策略。但更先进的制程长期以来代表着技术的领先性,以及更高的性能和更低的功耗,因此格外受到外界关注。

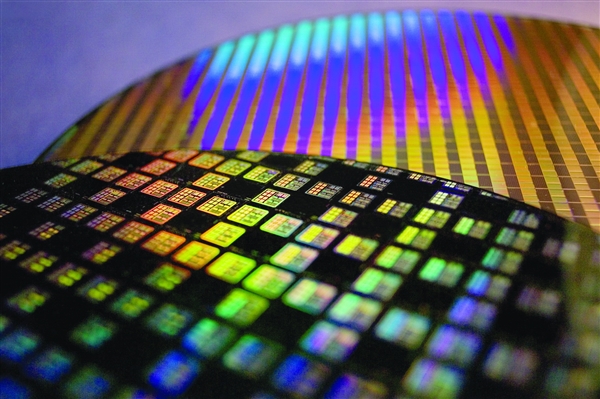

一般而言,新节点诞生的完整过程,需要经过前期研发和后期工厂验证,在风险试产的过程中逐渐提升良率,达到一定标准后才能正式量产,进入市场。

“通常而言良率要达到85%以上才能顺利量产,低良率不仅意味着亏损,也代表劣质低效,即便是最终被应用了,也可能出现异常,会给使用者带来不好的体验,所以良率是一个非常严肃的问题。”聚焦晶圆制造良率问题的中国企业众壹云的创始人之一、战略咨询专家李海俊告诉雷锋网。

不过,85%的良率并不是一个标准的参考线。半导体行业资深人士陈一(化名)向雷锋表示,工厂一般有大致达标的良率供参考,对于一定达到什么数值才能算真正进入量产,每个公司认定标准不同,除了良率,还要看良率的一致性。

专注帮助芯片设计公司以及晶圆制造厂改善良率的普迪飞半导体公司资深技术总监王健也向雷锋网(公众号:雷锋网)表示,不同的公司、不同的产品与设计不尽相同,没有放之四海而皆准的统一标准。“一般而言,手机等消费级产品量大,良率更高,汽车、航空等芯片产品其类制造流程中会做一些特定的改进,复杂的制造流程加上更加严格的指标和要求,导致其最终良率会比消费类低,售价也相应高一些。”王健补充到。

需要注意的是,虽然较低的芯片良率有可能会影响到最终的成品情况,但芯片良率与产品合格率有所区别。“芯片制造过程中会引入各种各样的不确定因素,流程缺陷、环境中的颗粒物、工艺的波动,最终生产出来的产品会有一些不确定性,最终的产品不满足这些指标就没办法正常交付,正常产品的占比就是良率。”王健说。

陈一对产品合格率加以解释,“我所理解的产品合格率,是一个质量概念,即卖出去的良品失效的比例,这是对封装工厂的重要考核指标,主要取决于工厂的技术和管理水平。”

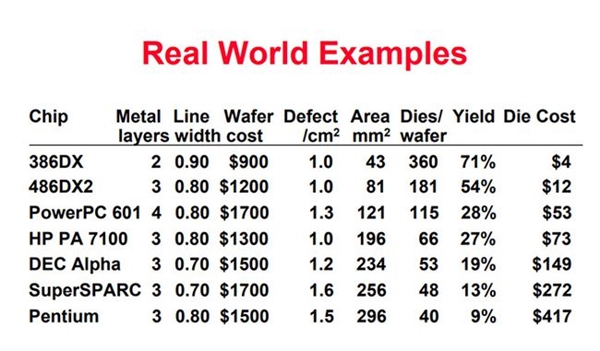

也就是说,如果按芯片制造流程来分,芯片设计和制造决定良率,封装测试决定产品最终的合格率。雷锋网了解到,芯片总良率是wafer良率、Die良率和封测良率的总乘积,影响芯片良率的因素复杂多样,一般而言设计越复杂、工艺步骤越多、制程偏移率越大,芯片良率越低,此外,环境污染也会对良率造成一定的影响。

对于芯片企业来说,芯片良率直接反应了所投放的芯片里可出售比例,因此也直接影响芯片制造成本。“从评估整个成本的角度来讲,良率是一个非常重要的指标,直接来说,良率直接影响到最终的实际成本,良率越高,最终实际分摊到每一颗正常芯片上的成本就越低。”王健说。

此前半导体材料厂商Entegris(应特格)执行副总裁及首席运营官Todd Edlund曾在接受媒体采访时表示,对于3D NAND晶圆厂而言,1%的良率提高可能意味着每年1.1亿美元的净利润;而对于尖端的逻辑晶圆厂而言,1%的良率提升意味着1.5亿美元的净利润。

之所以说提升芯片良率与制程开发同等重要,除了提升良率是芯片从实验室阶段到量产的必经之路以及芯片良率与整体成本密切相关之外,从经济角度上讲,提升芯片良率可以视为摩尔定律的另一种延续。

摩尔定律最早由英特尔创始人之一戈登摩尔在1965年提出,集成电路上可容纳的晶体管的数目每隔两年便会增加一倍。之后在众多专业人士的集思广益下得以延伸,两年缩短为18个月,晶体管数目的增加一倍也意味着微处理器性能提升一倍或价格下降一半。虽然一直以来被业界奉为圭臬,但追根到底,摩尔定律并非自然科学定律,而是摩尔的经验之谈,是集成电路领域的经济定律。

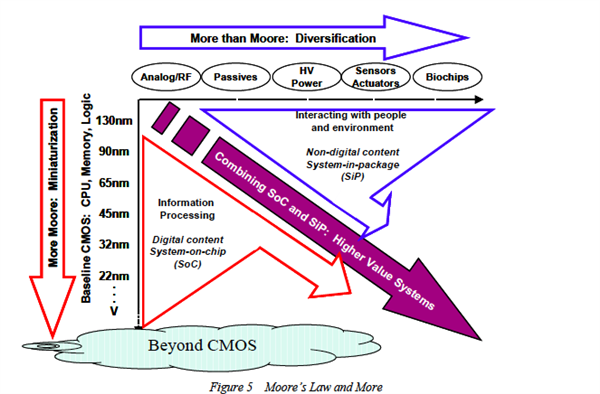

正在推动摩尔定律向前发展的,实际上是用更低的成本做出更好的产品。摩尔定律发展至今,无论是技术上还是资本上都已经举步维艰,IBS的数据显示,开发3nm芯片设计成本高达5.9亿美元,5nm器件的成本达4.16亿美元。因此衍生出超越摩尔定律(More than Moore),不再只局限于晶体管微缩,更优化的电路设计、系统算法以及异构集成都被纳入其中。按照这一逻辑,在非最先进制程上进一步提升芯片良率也可以被视为摩尔定律的延伸。

2005年,ITRS首次引入“More than Moore”(MtM)和“More Moore”(MM),图片源自IEEEE IRDS社区

王健告诉雷锋网,传统上业界习惯用PPA的方式去评估芯片设计上做出的一些决定,但大概在近20年左右的时间里,大家开始发现PPA无法非常全面地衡量芯片设计上一些决定以及最终对产品的影响,随之加入了一些其他标准,包括成本(C)、产品导入市场的时间(T),以及产品的可靠性(R),这些标准与良率直接相关。

值得注意的是,将其视为摩尔定律延伸的前提是:芯片良率多少并不直接决定晶圆厂是否进入到下一代工艺的研发。“新工艺的开发不是建立在前一工艺良率稳定的基础上,研发团队一直在挑战制程极限,”陈一说到。这也就是为什么芯片大厂在公布技术路线图时,往往出现同时研发多个工艺节点的情况。

如果进一步比较提升芯片良率与研发下一代制程哪一种路径性价比更高,李海俊认为前者更加实际有效,“除了手机电脑芯片,大部分智能应用场景所需的芯片可能连28nm的工艺都用不到,从性价比看根本不需要5nm以下的芯片,也就不需要花费动辄上亿美金开发先进制程,还有可能花了很多钱之后,做出来的概率依然很低,这是一个听起来让人绝望的怪路径,所以提高芯片良率更为实际有效,目前大部分学者也赞同这一方向,认为其符合内循环的政策引导。”

既然研发先进制程从经济上讲怪路径,为何芯片巨头们还在咬牙坚持,李海俊进一步解释,“站在产业链发展和国家利益来说,先进制程研发的步伐一刻不能停,半导体是赢家通吃的局面,落后只有死路一条。这事关市场和地位争夺、国家安全和民生安全,虽然是充满挑战的怪路径,但催人振奋。”

如果将先进制程的研发视为芯片巨头们之间的竞争,那么提高芯片良率则可以视为芯片厂商的自我竞赛,一方面是因为良率作为芯片厂商的最高机密数据十分敏感,不会像公布工艺节点那样公布自家真实良率情况,另一方面是影响良率的因素众多,很难有一个准确的数值与竞争对手进行比较,而芯片厂商始终致力于能够在短时间内就向客户交付安全正常的芯片,提升良率需要争分夺秒。

“对芯片设计公司而言,如何更加高效地提升产品良率,如何把经验传承到下一代产品设计中去是需要思考的问题,对于芯片制造公司而言,如何更快地完成工艺研发使得能够更早地引入客户,以及如何帮助客户更快地提升良率是需要思考的问题,”王健告诉雷锋网。

随着半导体行业逐渐发生变化,尤其是从IDM向Fabless、Foundry等经营模式延伸,业界提升芯片良率所面临的难题及措施都在相应地发生改变。

“芯片的良率取决于两个因素,一是产品对工艺的需求和工艺能够满足两者之间的匹配度,而是产品工程师和产线工艺工程师的沟通是否到位。”陈一说到。

也就是说,作为芯片公司的自我较量,芯片良率需要芯片设计公司和芯片制造公司的紧密配合和有效沟通才能得以最终保障。这一沟通与配合在IDM时代实现更容易,在Fabless、Foundry盛行的今天却面临一些难题。

尤其是在工艺研发阶段,芯片公司无法穷尽所有版图图形组合做完整的评估,而在设计公司提交的设计中,某些特定的图形组合将触发特定的问题,这需要用借用第三方大数据平台分析。

也正因如此,在半导体产业近10年至20年的发展过程中,逐渐诞生了类似普迪飞、众壹云等帮助芯片设计公司和芯片制造公司更加高效合作以提升芯片良率的公司,作为产业链中一个新环节出现,为半导体公司提供大数据分析平台,或提供面向缺陷和良率管理的套件组合。

在帮助芯片厂商改善良率的过程中,这一“新环节”上的公司前期主要关注整个良率的评估,将良率水平的差距分解到具体的工艺或设计上,同设计厂或制造厂共同合作在短时间内改善良率,当良率达到理想水平后,便将注意力更多地放在维持量产监控以及预防上。

提升良率,作为芯片厂商的一场自我较量,虽然很难以具体的数值占比来评估其重要性,但它贯穿产业链的上下游,贯穿一颗芯片的生命周期,业界普遍将其视为芯片制造的终极挑战,是芯片厂商自始至终都需要面临的问题。

“芯片良率问题,直接对应的是工艺、设备、材料的问题,在这之后是管理的问题、商业模式的问题,人才的问题、开放式创新的问题。”李海俊说到。

支付宝扫一扫

支付宝扫一扫 微信扫一扫

微信扫一扫