PCIe 6.0 0.71版草案即将完成:年底正式发布 带宽256GB/s

PCIe 4.0正在逐渐普及,PCIe 5.0即将在Intel Sapphire Rapids下代至强、Alder Lake下代酷睿上落地,PCIe 6.0也在有序推进之中。

PCIe 6.0 0.7版草案在去年11月完成并发放给组织会员,PCI-SIG目前仍在搜集整理反馈,计划在下个月发布0.71版草案,并入0.7版草案以来的所有新协议、电气规格更新,但变化不会太大。

0.71版草案有30天的评估期,如果没什么问题的话就将转入0.9版草案,也是正式版之前的最后一步。

PCI-SIG组织对于PCIe 6.0标准非常兴奋,认为它堪比PCIe 2.0向PCIe 3.0的升级,后者是PCIe历史上寿命最长的一代标准。

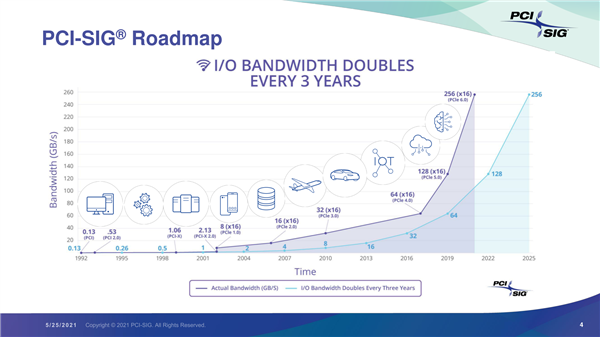

PCIe 6.0按照传统继续让I/O带宽翻番达到64GT/s,应用到实际中,PCIe 6.0 x1单向实际带宽8GB/s,PCIe 6.0 x16单向带宽128GB/s、双向带宽256GB/s。

如今广泛使用的PCIe 4.0 x4 SSD,到时候只需要PCIe 6.0 x1就可以搞定。

PCIe 6.0将延续PCIe 3.0时代引入的128b/130b编码方式,但加入全新的脉冲幅度调制PAM4,取代PCIe 5.0 NRZ,可以在单个通道、同样时间内封包更多数据,以及低延迟前向纠错(FEC)和相关机制,以改进带宽效率。

很多人可能会疑问,PCIe 3.0的带宽很多时候都用不完,PCIe 6.0有啥用?显然不是给消费级市场准备的,甚至不是一般的企业级、数据中心级应用,而是针对云端、人工智能、机器学习、边缘计算等需要超高带宽的领域,单个PCIe 6.0 x16就可以支持800G以太网,还有各种加速器、FPGA、ASIC、存储等等。

支付宝扫一扫

支付宝扫一扫 微信扫一扫

微信扫一扫