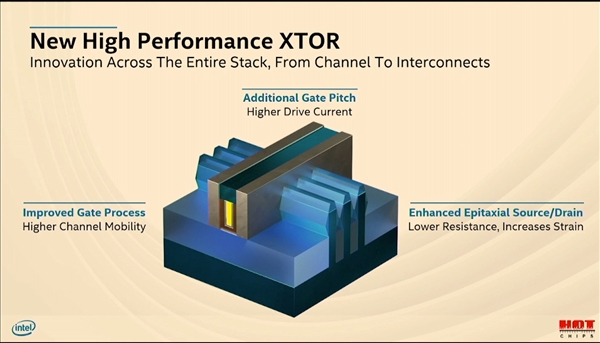

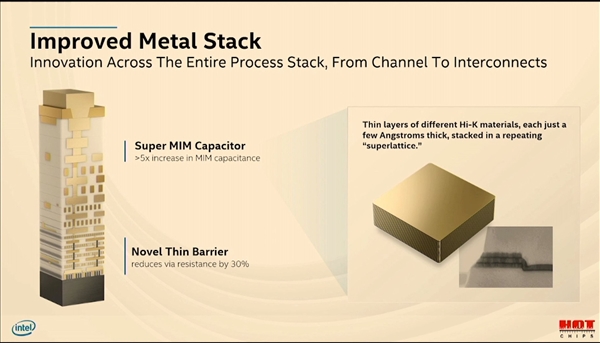

日前的2020年度架构日上,Intel首次公开介绍了,以及所用的,可以理解为10nm++版本。

HotChips 2020半导体大会上,Intel又一次公开讲解了Tiger Lake的架构设计,并第一次亮出了Tiger Lake的晶圆:

唯一可惜的,这次是线上会议,晶圆也只能通过视频欣赏一下,看不到近处细节,不能数一数一块晶圆能产出多少芯片,自然无法估算大致面积。

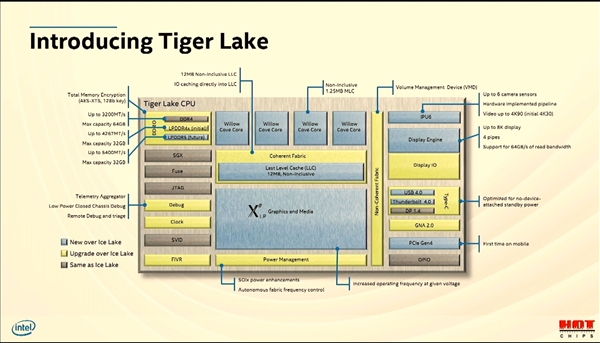

Tiger Lake架构、10nm SuperFin工艺的具体特点就不重复了,只看一张Tiger Lake架构的整体图:

其中,标注蓝色的部分是全新增加的,黄色是在Ice Lake基础上升级的,灰色部分则是和Ice Lake完全一致,而这部分是最少的,而且都是一些无关紧要的模块,进一步验证了Tiger Lake架构的变革之大。

1.25MB每核心二级缓存、12MB三级缓存、Xe GPU核显、多媒体引擎、显示引擎、32GB LPDDR5-5400内存支持(后期升级)、IPU6图像处理单元、PCIe 4.0(移动平台第一次)、USB4、Thunderbolt 4。

32GB LPDDR4X-4267内存、一致性缓存结构、显示输入输出、USB Type-C输出、高斯网络加速器GAN 2.0、电源管理、FIVR(全集成电压稳压器)、调试与时钟模块。

64GB DDR4-3200内存、SGX、OPIO。

支付宝扫一扫

支付宝扫一扫 微信扫一扫

微信扫一扫